[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 1/8] [RISCV] Add support for getHostCPUFeatures using hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap &Features) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap &Features) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap &Features) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 2/8] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap &Features)

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap &Features) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Re

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 1/9] [RISCV] Add support for getHostCPUFeatures using hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap &Features) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap &Features) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap &Features) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 2/9] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap &Features)

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap &Features) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Re

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

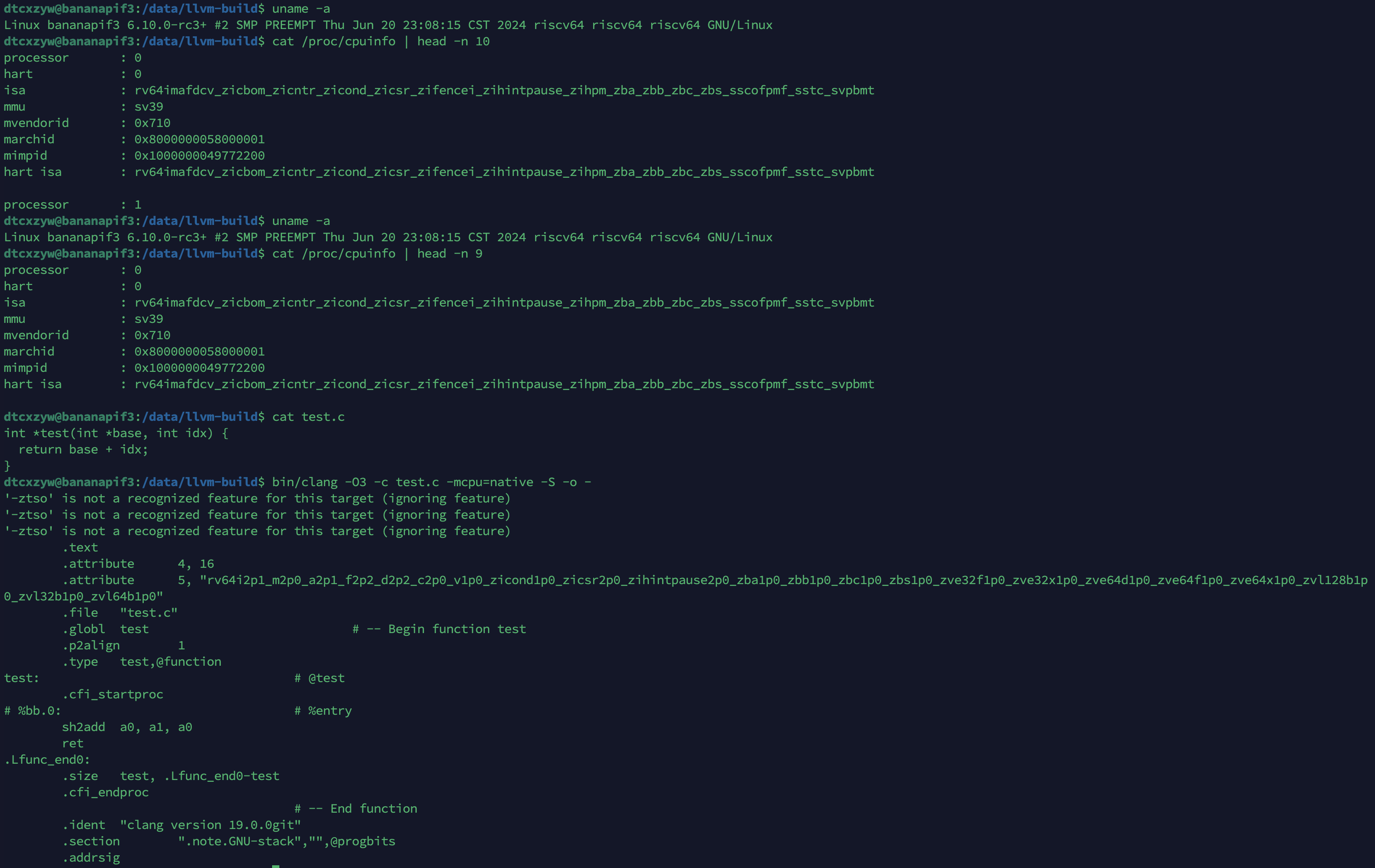

dtcxzyw wrote: > > I have no idea about why it corrupts StringMap. Sad :( > >  > > Is this fixed after fixing the return statement? This may be caused by the > corruption of `getHostCPUNameForRISCV`.  It works well now :) I will post a patch removing experimental from `ztso`. https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Remove experimental from Ztso. (PR #96465)

https://github.com/dtcxzyw created

https://github.com/llvm/llvm-project/pull/96465

Ztso 1.0 was ratified in January 2023.

Documentation:

https://github.com/riscv/riscv-isa-manual/blob/main/src/ztso-st-ext.adoc

>From 34670ab55ccecb1a2c7d92f809c9cae0df4150c6 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Mon, 24 Jun 2024 16:43:04 +0800

Subject: [PATCH] [RISCV] Remove experimental from Ztso.

---

clang/test/Driver/riscv-arch.c| 24 ++

.../test/Preprocessor/riscv-target-features.c | 10 ++--

llvm/docs/RISCVUsage.rst | 4 +-

llvm/docs/ReleaseNotes.rst| 1 +

llvm/lib/Target/RISCV/RISCVFeatures.td| 4 +-

.../CodeGen/RISCV/GlobalISel/atomic-fence.ll | 4 +-

llvm/test/CodeGen/RISCV/atomic-cmpxchg.ll | 10 ++--

llvm/test/CodeGen/RISCV/atomic-fence.ll | 4 +-

llvm/test/CodeGen/RISCV/atomic-load-store.ll | 8 ++--

llvm/test/CodeGen/RISCV/atomic-rmw.ll | 12 ++---

.../CodeGen/RISCV/atomicrmw-uinc-udec-wrap.ll | 4 +-

llvm/test/CodeGen/RISCV/attributes.ll | 4 +-

llvm/test/CodeGen/RISCV/module-elf-flags.ll | 2 +-

llvm/test/MC/RISCV/Ztso.s | 4 +-

llvm/test/MC/RISCV/attribute-arch.s | 4 +-

llvm/test/MC/RISCV/elf-flags.s| 4 +-

.../TargetParser/RISCVISAInfoTest.cpp | 46 +--

17 files changed, 77 insertions(+), 72 deletions(-)

diff --git a/clang/test/Driver/riscv-arch.c b/clang/test/Driver/riscv-arch.c

index ffd92e1f398c4..c3c471c4bc396 100644

--- a/clang/test/Driver/riscv-arch.c

+++ b/clang/test/Driver/riscv-arch.c

@@ -365,24 +365,30 @@

// RUN: -fsyntax-only 2>&1 | FileCheck -check-prefix=RV32-ZFHMIN %s

// RV32-ZFHMIN: "-target-feature" "+zfhmin"

-// RUN: not %clang --target=riscv32-unknown-elf -march=rv32iztso -### %s \

+// RUN: not %clang --target=riscv32-unknown-elf -march=rv32izalasr -### %s \

// RUN: -fsyntax-only 2>&1 | FileCheck -check-prefix=RV32-EXPERIMENTAL-NOFLAG

%s

-// RV32-EXPERIMENTAL-NOFLAG: error: invalid arch name 'rv32iztso'

+// RV32-EXPERIMENTAL-NOFLAG: error: invalid arch name 'rv32izalasr'

// RV32-EXPERIMENTAL-NOFLAG: requires '-menable-experimental-extensions'

-// RUN: not %clang --target=riscv32-unknown-elf -march=rv32iztso

-menable-experimental-extensions -### %s \

+// RUN: not %clang --target=riscv32-unknown-elf -march=rv32izalasr

-menable-experimental-extensions -### %s \

// RUN: -fsyntax-only 2>&1 | FileCheck -check-prefix=RV32-EXPERIMENTAL-NOVERS

%s

-// RV32-EXPERIMENTAL-NOVERS: error: invalid arch name 'rv32iztso'

+// RV32-EXPERIMENTAL-NOVERS: error: invalid arch name 'rv32izalasr'

// RV32-EXPERIMENTAL-NOVERS: experimental extension requires explicit version

number

-// RUN: not %clang --target=riscv32-unknown-elf -march=rv32iztso0p7

-menable-experimental-extensions -### %s \

+// RUN: not %clang --target=riscv32-unknown-elf -march=rv32izalasr0p7

-menable-experimental-extensions -### %s \

// RUN: -fsyntax-only 2>&1 | FileCheck -check-prefix=RV32-EXPERIMENTAL-BADVERS

%s

-// RV32-EXPERIMENTAL-BADVERS: error: invalid arch name 'rv32iztso0p7'

-// RV32-EXPERIMENTAL-BADVERS: unsupported version number 0.7 for experimental

extension 'ztso' (this compiler supports 0.1)

+// RV32-EXPERIMENTAL-BADVERS: error: invalid arch name 'rv32izalasr0p7'

+// RV32-EXPERIMENTAL-BADVERS: unsupported version number 0.7 for experimental

extension 'zalasr' (this compiler supports 0.1)

-// RUN: %clang --target=riscv32-unknown-elf -march=rv32iztso0p1

-menable-experimental-extensions -### %s \

+// RUN: %clang --target=riscv32-unknown-elf -march=rv32izalasr0p1

-menable-experimental-extensions -### %s \

// RUN: -fsyntax-only 2>&1 | FileCheck

-check-prefix=RV32-EXPERIMENTAL-GOODVERS %s

-// RV32-EXPERIMENTAL-GOODVERS: "-target-feature" "+experimental-ztso"

+// RV32-EXPERIMENTAL-GOODVERS: "-target-feature" "+experimental-zalasr"

+

+// RUN: %clang --target=riscv32-unknown-elf -march=rv32iztso1p0 -### %s \

+// RUN: -fsyntax-only 2>&1 | FileCheck -check-prefix=RV32-ZTSO %s

+// RUN: %clang --target=riscv32-unknown-elf -march=rv32iztso -### %s \

+// RUN: -fsyntax-only 2>&1 | FileCheck -check-prefix=RV32-ZTSO %s

+// RV32-ZTSO: "-target-feature" "+ztso"

// RUN: %clang --target=riscv32-unknown-elf -march=rv32izbb1p0 -### %s \

// RUN: -fsyntax-only 2>&1 | FileCheck -check-prefix=RV32-ZBB %s

diff --git a/clang/test/Preprocessor/riscv-target-features.c

b/clang/test/Preprocessor/riscv-target-features.c

index d7935af532dfa..46a61e3c0afc7 100644

--- a/clang/test/Preprocessor/riscv-target-features.c

+++ b/clang/test/Preprocessor/riscv-target-features.c

@@ -1650,13 +1650,13 @@

// RUN: -o - | FileCheck --check-prefix=CHECK-ZICFILP-EXT %s

// CHECK-ZICFILP-EXT: __riscv_zicfilp 4000{{$}}

-// RUN: %clang --target=riscv32-unknown-linux-gnu

-menable-experimental-extensions \

-// RUN: -march=rv32iztso0p1 -E -dM %s \

+// RUN: %clang --target=riscv32-unknown-linux-gnu \

+// RUN: -march=rv32iztso1p0 -E -dM %s \

// R

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

dtcxzyw wrote: See https://github.com/llvm/llvm-project/pull/96465 https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Remove experimental from Ztso. (PR #96465)

@@ -365,24 +365,30 @@ // RUN: -fsyntax-only 2>&1 | FileCheck -check-prefix=RV32-ZFHMIN %s // RV32-ZFHMIN: "-target-feature" "+zfhmin" -// RUN: not %clang --target=riscv32-unknown-elf -march=rv32iztso -### %s \ +// RUN: not %clang --target=riscv32-unknown-elf -march=rv32izalasr -### %s \ dtcxzyw wrote: Yeah. https://github.com/llvm/llvm-project/pull/96465 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Remove experimental from Ztso. (PR #96465)

https://github.com/dtcxzyw closed https://github.com/llvm/llvm-project/pull/96465 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/10] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap &Features) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap &Features) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap &Features) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/10] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap &Features)

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap &Features) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ i

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/11] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap &Features) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap &Features) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap &Features) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/11] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap &Features)

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap &Features) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ i

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap &Features) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap &Features) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

+/*pair_count=*/std::size(Query), /*cpu_count=*/0,

+/*cpus=*/0, /*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t BaseMask = Query[0].Value;

+ // Check whether RISCV_HWPROBE_BASE_BEHAVIOR_IMA is set.

+ if (BaseMask & 1) {

+Features["i"] = true;

+Features["m"] = true;

+Features["a"] = true;

+ }

+

+ uint64_t ExtMask = Query[1].Value;

+ Features["f"] = ExtMask & (1 << 0); // RISCV_HWPROBE_IMA_FD

+ Features["d"] = ExtMask & (1 << 0); // RISCV_HWPROBE_IMA_FD

+ Features["c"] = ExtMask & (1 << 1); // RISCV_HWPROBE_IMA_C

+ Features["v"] = ExtMask & (1 << 2); // RISCV_HWPROBE_IMA_V

+ Features["zba"] = ExtMask & (1 << 3); // RISCV_HWPROBE_EXT_ZBA

+ Features["zbb"] = ExtMask & (1 << 4); // RISCV_HWPROBE_EXT_ZBB

+ Features["zbs"] = ExtMask & (1 << 5); // RISCV_HWPROBE_EXT_ZBS

+ Features["zicboz"] = ExtMask & (1 << 6); // RISCV_HWPROBE_EXT_ZICBOZ

+ Features["zbc"] = ExtMask & (1 << 7); // RISCV_HWPROBE_EXT_ZBC

+ Features["zbkb"] = ExtMask & (1 << 8);// RISCV_HWPROBE_EXT_ZBKB

+ Features["zbkc"] = ExtMask & (1 << 9);// RISCV_HWPROBE_EXT_ZBKC

+ Features["zbkx"] = ExtMask & (1 << 10); // RISCV_HWPROBE_EXT_ZBKX

+ Features["zknd"] = ExtMask & (1 << 11); // RISCV_HWPROBE_EXT_ZKND

+ Features["zkne"] = ExtMask & (1 << 12); // RISCV_HWPROBE_EXT_ZKNE

+ Features["zknh"] = ExtMask & (1 << 13); // RISCV_HWPROBE_EXT_ZKNH

+ Features["zksed"] = ExtMask & (1 << 14); // RISCV_HWPROBE_EXT_ZKSED

+ Features["zksh"] = ExtMask & (1 << 15); // RISCV_HWPROBE_EXT_ZKSH

+ Features["zkt"] = ExtMask & (1 << 16);// RISCV_HWPROBE_EXT_ZKT

+ Features["zvbb"] = ExtMask & (1 << 17); // RISCV_HWPROBE_EXT_ZVBB

+ Features["zvbc"] = ExtMask & (1 << 18); // RISCV_HWPROBE_EXT_ZVBC

+ Features["zvkb"] = ExtMask & (1 << 19); // RISCV_HWPROBE_EXT_ZVKB

+ Features["zvkg"] = ExtMask & (1 << 20); // RISCV_HWPROBE_EXT_ZVKG

+ Features["zvkned"] = ExtMask & (1 << 21); // RISCV_HWPROBE_EXT_ZVKNED

+ Features["zvknha"] = ExtMask & (1 << 22); // RISCV_HWPROBE_EXT_ZVKNHA

+ Features["zvknhb"] = ExtMask & (1 << 23); // RISCV_HWPROBE_EXT_ZVKNHB

+ Features["zvksed"] = ExtMask & (1 << 24); // RISCV_HWPROBE_EXT_ZVKSED

+ Features["zvksh"] = ExtMask & (1 << 25); // RISCV_HWPROBE_EXT_ZVKSH

+ Features["zvkt"] = ExtMask & (1 << 26); // RISCV_HWPROBE_EXT_ZVKT

+ Features["zfh"] = ExtMask & (1 << 27);// RISCV_HWPROBE_EXT_ZFH

+ Features["zfhmin"] = ExtMask & (1 << 28); // RISCV_HWPROBE_EXT_ZFHMIN

+ Features["zihintntl"] = ExtMask & (1 << 29); // RISCV_HWPROBE_EXT_ZIHINTNTL

+ Features["zvfh"] = ExtMask & (1 << 30); // RISCV_HWPROBE_EXT_ZVFH

+ Features["zvfhmin"] = ExtMask & (1ULL << 31); // RISCV_HWPROBE_EXT_ZVFHMIN

+ Features["zfa"] = ExtMask & (1ULL << 32); // RISCV_HWPROBE_EXT_ZFA

+ // TODO: set ztso when it is no longer experimental.

+ // Features["ztso"] = ExtMask & (1ULL << 33);// RISCV_HWPROBE_EXT_ZTSO

dtcxzyw wrote:

@topperc @preames What do you think about the ztso support as a todo?

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw edited https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap &Features) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap &Features) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

+/*pair_count=*/std::size(Query), /*cpu_count=*/0,

+/*cpus=*/0, /*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t BaseMask = Query[0].Value;

+ // Check whether RISCV_HWPROBE_BASE_BEHAVIOR_IMA is set.

+ if (BaseMask & 1) {

+Features["i"] = true;

+Features["m"] = true;

+Features["a"] = true;

+ }

+

+ uint64_t ExtMask = Query[1].Value;

+ Features["f"] = ExtMask & (1 << 0); // RISCV_HWPROBE_IMA_FD

+ Features["d"] = ExtMask & (1 << 0); // RISCV_HWPROBE_IMA_FD

+ Features["c"] = ExtMask & (1 << 1); // RISCV_HWPROBE_IMA_C

+ Features["v"] = ExtMask & (1 << 2); // RISCV_HWPROBE_IMA_V

+ Features["zba"] = ExtMask & (1 << 3); // RISCV_HWPROBE_EXT_ZBA

+ Features["zbb"] = ExtMask & (1 << 4); // RISCV_HWPROBE_EXT_ZBB

+ Features["zbs"] = ExtMask & (1 << 5); // RISCV_HWPROBE_EXT_ZBS

+ Features["zicboz"] = ExtMask & (1 << 6); // RISCV_HWPROBE_EXT_ZICBOZ

+ Features["zbc"] = ExtMask & (1 << 7); // RISCV_HWPROBE_EXT_ZBC

+ Features["zbkb"] = ExtMask & (1 << 8);// RISCV_HWPROBE_EXT_ZBKB

+ Features["zbkc"] = ExtMask & (1 << 9);// RISCV_HWPROBE_EXT_ZBKC

+ Features["zbkx"] = ExtMask & (1 << 10); // RISCV_HWPROBE_EXT_ZBKX

+ Features["zknd"] = ExtMask & (1 << 11); // RISCV_HWPROBE_EXT_ZKND

+ Features["zkne"] = ExtMask & (1 << 12); // RISCV_HWPROBE_EXT_ZKNE

+ Features["zknh"] = ExtMask & (1 << 13); // RISCV_HWPROBE_EXT_ZKNH

+ Features["zksed"] = ExtMask & (1 << 14); // RISCV_HWPROBE_EXT_ZKSED

+ Features["zksh"] = ExtMask & (1 << 15); // RISCV_HWPROBE_EXT_ZKSH

+ Features["zkt"] = ExtMask & (1 << 16);// RISCV_HWPROBE_EXT_ZKT

+ Features["zvbb"] = ExtMask & (1 << 17); // RISCV_HWPROBE_EXT_ZVBB

+ Features["zvbc"] = ExtMask & (1 << 18); // RISCV_HWPROBE_EXT_ZVBC

+ Features["zvkb"] = ExtMask & (1 << 19); // RISCV_HWPROBE_EXT_ZVKB

+ Features["zvkg"] = ExtMask & (1 << 20); // RISCV_HWPROBE_EXT_ZVKG

+ Features["zvkned"] = ExtMask & (1 << 21); // RISCV_HWPROBE_EXT_ZVKNED

+ Features["zvknha"] = ExtMask & (1 << 22); // RISCV_HWPROBE_EXT_ZVKNHA

+ Features["zvknhb"] = ExtMask & (1 << 23); // RISCV_HWPROBE_EXT_ZVKNHB

+ Features["zvksed"] = ExtMask & (1 << 24); // RISCV_HWPROBE_EXT_ZVKSED

+ Features["zvksh"] = ExtMask & (1 << 25); // RISCV_HWPROBE_EXT_ZVKSH

+ Features["zvkt"] = ExtMask & (1 << 26); // RISCV_HWPROBE_EXT_ZVKT

+ Features["zfh"] = ExtMask & (1 << 27);// RISCV_HWPROBE_EXT_ZFH

+ Features["zfhmin"] = ExtMask & (1 << 28); // RISCV_HWPROBE_EXT_ZFHMIN

+ Features["zihintntl"] = ExtMask & (1 << 29); // RISCV_HWPROBE_EXT_ZIHINTNTL

+ Features["zvfh"] = ExtMask & (1 << 30); // RISCV_HWPROBE_EXT_ZVFH

+ Features["zvfhmin"] = ExtMask & (1ULL << 31); // RISCV_HWPROBE_EXT_ZVFHMIN

+ Features["zfa"] = ExtMask & (1ULL << 32); // RISCV_HWPROBE_EXT_ZFA

+ // TODO: set ztso when it is no longer experimental.

+ // Features["ztso"] = ExtMask & (1ULL << 33);// RISCV_HWPROBE_EXT_ZTSO

dtcxzyw wrote:

Hwprobe docs says the core supports Ztso ***v1.0*** when RISCV_HWPROBE_EXT_ZTSO

is set.

> RISCV_HWPROBE_EXT_ZTSO: The Ztso extension is supported as

defined in the RISC-V ISA manual starting from [commit

5618fb5a216b](https://github.com/riscv/riscv-isa-manual/commit/5618fb5a216b6eb76cbd2b1c8e3d1b55628a072a)

(“Ztso is now ratified.”)

I don't think it's appropriate to add experimental features for users.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap &Features) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap &Features) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

+/*pair_count=*/std::size(Query), /*cpu_count=*/0,

+/*cpus=*/0, /*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t BaseMask = Query[0].Value;

+ // Check whether RISCV_HWPROBE_BASE_BEHAVIOR_IMA is set.

+ if (BaseMask & 1) {

+Features["i"] = true;

+Features["m"] = true;

+Features["a"] = true;

+ }

+

+ uint64_t ExtMask = Query[1].Value;

dtcxzyw wrote:

FYI, openjdk still uses the value in `RISCV_HWPROBE_KEY_IMA_EXT_0` even if

`RISCV_HWPROBE_BASE_BEHAVIOR_IMA` is not set.

See

https://github.com/openjdk/jdk/blob/e527e1c32fcc7b2560cec540bcde930075ac284a/src/hotspot/os_cpu/linux_riscv/riscv_hwprobe.cpp#L142-L185.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

dtcxzyw wrote: Any thoughts? Hopefully I can catch up with the 19 release :) https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap &Features) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap &Features) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

dtcxzyw wrote:

Currently `sys::getHostCPUFeatures` has three callers:

+ clang -> `riscv::getRISCVTargetFeatures`

+ llvm-tools -> `codegen::getFeaturesStr`

+ JIT users -> `JITTargetMachineBuilder::detectHost`

I don't think there are any opportunities to reuse the result.

BTW, https://github.com/llvm/llvm-project/pull/85790 may benefit from the vDSO

symbol, but it implements caching itself.

I didn't use the glibc call `__riscv_hwprobe` since `sys/hwprobe.h` was

unavailable on my RV board :(

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -83,8 +83,14 @@ void riscv::getRISCVTargetFeatures(const Driver &D, const

llvm::Triple &Triple,

// and other features (ex. mirco architecture feature) from mcpu

if (Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ llvm::StringMap HostFeatures;

+ if (llvm::sys::getHostCPUFeatures(HostFeatures))

+for (auto &F : HostFeatures)

+ Features.push_back(

+ Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+}

dtcxzyw wrote:

@wangpc-pp @topperc

Are there any equivalents of the helper `printMArch`?

https://github.com/llvm/llvm-project/blob/ba60d8a11af2cdd7e80e2fd968cdf52adcabf5a1/llvm/utils/TableGen/RISCVTargetDefEmitter.cpp#L90-L123

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [Pipelines] Move IPSCCP after inliner pipeline (PR #96620)

dtcxzyw wrote: > This patch causes some significant performance regressions on llvm-test-suite > (rv64gc-O3-thinlto): > > Name Before After Ratio > SingleSource/Benchmarks/Shootout/Shootout-random 2.150161677 > 3.300161641 + 53.5% > SingleSource/Benchmarks/Polybench/linear-algebra/kernels/trisolv/trisolv > 0.111845159 0.145389494 +30.0% > SingleSource/Benchmarks/Adobe-C++/functionobjects 5.489498263 > 6.827863965 +24.4% It has been fixed. But this patch didn't show a positive net effect :( https://github.com/llvm/llvm-project/pull/96620 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [Pipelines] Move IPSCCP after inliner pipeline (PR #96620)

dtcxzyw wrote: > Does that mean it has a negative net effect, or its neutral It is neutral. > (in which case the original motivating case should be enough). But this patch may have an impact on compile time. https://github.com/llvm/llvm-project/pull/96620 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/12] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap &Features) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap &Features) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap &Features) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/12] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap &Features)

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap &Features) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ i

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -83,8 +83,14 @@ void riscv::getRISCVTargetFeatures(const Driver &D, const

llvm::Triple &Triple,

// and other features (ex. mirco architecture feature) from mcpu

if (Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ llvm::StringMap HostFeatures;

+ if (llvm::sys::getHostCPUFeatures(HostFeatures))

+for (auto &F : HostFeatures)

+ Features.push_back(

+ Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+}

dtcxzyw wrote:

Done.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -83,8 +83,14 @@ void riscv::getRISCVTargetFeatures(const Driver &D, const

llvm::Triple &Triple,

// and other features (ex. mirco architecture feature) from mcpu

if (Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ llvm::StringMap HostFeatures;

+ if (llvm::sys::getHostCPUFeatures(HostFeatures))

+for (auto &F : HostFeatures)

+ Features.push_back(

+ Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+}

dtcxzyw wrote:

See

https://github.com/llvm/llvm-project/blob/0f5fa3558eb36823c16ba81a4c6e6e23a5f9df24/clang/lib/Driver/ToolChains/Arch/RISCV.cpp#L72-L78.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -290,8 +290,24 @@ StringRef riscv::getRISCVArch(const llvm::opt::ArgList

&Args,

// 2. Get march (isa string) based on `-mcpu=`

if (const Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ // If the target cpu is unrecognized, use target features.

+ if (CPU.empty() || CPU.starts_with("generic")) {

+llvm::StringMap HostFeatures;

+if (llvm::sys::getHostCPUFeatures(HostFeatures)) {

+ std::vector Features;

+ for (auto &F : HostFeatures)

+Features.push_back(

+Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+

+ auto ParseResult = llvm::RISCVISAInfo::parseFeatures(

+ Triple.isRISCV32() ? 32 : 64, Features);

+ if (ParseResult)

+return (*ParseResult)->toString();

dtcxzyw wrote:

Sorry, I forget that `riscv::getRISCVArch` returns `StringRef`.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/13] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap &Features) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap &Features) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap &Features) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/13] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap &Features)

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap &Features) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/&Query,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ i

[clang] [InstCombine] Add combines/simplifications for `llvm.ptrmask` (PR #67166)

@@ -1964,18 +1964,78 @@ Instruction *InstCombinerImpl::visitCallInst(CallInst

&CI) {

break;

}

case Intrinsic::ptrmask: {

+KnownBits Known(DL.getPointerTypeSizeInBits(II->getType()));

+if (SimplifyDemandedInstructionBits(*II, Known))

+ return II;

+

+Value *Op0 = II->getArgOperand(0);

+Value *Op1 = II->getArgOperand(1);

+// Fail loudly in case this is ever changed.

+// TODO: If vector types are supported the merging of (ptrmask (ptrmask))

+// need to ensure we don't merge a vectype with non-vec type.

+assert(!Op0->getType()->isVectorTy() && !Op1->getType()->isVectorTy() &&

+ "These combines where written at a time when ptrmask did not "

+ "support vector types and may not work for vectors");

+

Value *InnerPtr, *InnerMask;

-if (match(II->getArgOperand(0),

- m_OneUse(m_Intrinsic(m_Value(InnerPtr),

- m_Value(InnerMask) {

- if (II->getArgOperand(1)->getType() == InnerMask->getType()) {

-Value *NewMask = Builder.CreateAnd(II->getArgOperand(1), InnerMask);

-return replaceInstUsesWith(

-*II,

-Builder.CreateIntrinsic(InnerPtr->getType(), Intrinsic::ptrmask,

-{InnerPtr, NewMask}));

+bool Changed = false;

+// Combine:

+// (ptrmask (ptrmask p, A), B)

+//-> (ptrmask p, (and A, B))

+if (match(Op0, m_OneUse(m_Intrinsic(

+ m_Value(InnerPtr), m_Value(InnerMask) {

+ // See if combining the two masks is free.

+ bool OkayToMerge = InnerMask->getType() == Op1->getType();

+ bool NeedsNew = false;

+ if (!OkayToMerge) {

+if (match(InnerMask, m_ImmConstant())) {

+ InnerMask = Builder.CreateZExtOrTrunc(InnerMask, Op1->getType());

+ OkayToMerge = true;

+} else if (match(Op1, m_ImmConstant())) {

+ Op1 = Builder.CreateZExtOrTrunc(Op1, InnerMask->getType());

+ OkayToMerge = true;

+ // Need to create a new one here, as the intrinsic id needs to

change.

+ NeedsNew = true;

+}

+ }

+ if (InnerMask->getType() == Op1->getType()) {

dtcxzyw wrote:

`OkayToMerge` is unused?

https://github.com/llvm/llvm-project/pull/67166

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [ValueTracking] Simplify uaddo pattern (PR #65910)

https://github.com/dtcxzyw updated https://github.com/llvm/llvm-project/pull/65910 >From 9bb817aa40dd9bc1bbb18b4cf4bc079145c8ecaa Mon Sep 17 00:00:00 2001 From: Yingwei Zheng Date: Mon, 11 Sep 2023 03:58:02 +0800 Subject: [PATCH 1/2] [ValueTracking] Simplify uaddo pattern --- llvm/lib/Analysis/ValueTracking.cpp | 23 .../InstSimplify/and-or-implied-cond.ll | 104 ++ 2 files changed, 127 insertions(+) diff --git a/llvm/lib/Analysis/ValueTracking.cpp b/llvm/lib/Analysis/ValueTracking.cpp index c4153b824c37e0a..5aaff4ee81be969 100644 --- a/llvm/lib/Analysis/ValueTracking.cpp +++ b/llvm/lib/Analysis/ValueTracking.cpp @@ -8291,6 +8291,29 @@ static std::optional isImpliedCondICmps(const ICmpInst *LHS, if (L0 == R0 && match(L1, m_APInt(LC)) && match(R1, m_APInt(RC))) return isImpliedCondCommonOperandWithConstants(LPred, *LC, RPred, *RC); + // L0 = R0 = L1 + R1, L0 >=u L1 implies R0 >=u R1, L0 From 83fa03f89c69a0a13336f6761023bb1415f92505 Mon Sep 17 00:00:00 2001 From: Yingwei Zheng Date: Sun, 24 Sep 2023 17:04:32 +0800 Subject: [PATCH 2/2] fixup! [ValueTracking] Simplify uaddo pattern --- llvm/lib/Analysis/ValueTracking.cpp | 2 +- 1 file changed, 1 insertion(+), 1 deletion(-) diff --git a/llvm/lib/Analysis/ValueTracking.cpp b/llvm/lib/Analysis/ValueTracking.cpp index 5aaff4ee81be969..f2278f3b7097dac 100644 --- a/llvm/lib/Analysis/ValueTracking.cpp +++ b/llvm/lib/Analysis/ValueTracking.cpp @@ -8308,7 +8308,7 @@ static std::optional isImpliedCondICmps(const ICmpInst *LHS, RPred = ICmpInst::getSwappedPredicate(RPred); } if (L0 == R0 && -(LPred == ICmpInst::ICMP_UGE || LPred == ICmpInst::ICMP_ULT) && +(LPred == ICmpInst::ICMP_ULT || LPred == ICmpInst::ICMP_UGE) && (RPred == ICmpInst::ICMP_ULT || RPred == ICmpInst::ICMP_UGE) && match(L0, m_c_Add(m_Specific(L1), m_Specific(R1 return LPred == RPred; ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang-tools-extra] [ValueTracking] Simplify uaddo pattern (PR #65910)

https://github.com/dtcxzyw updated https://github.com/llvm/llvm-project/pull/65910 >From 9bb817aa40dd9bc1bbb18b4cf4bc079145c8ecaa Mon Sep 17 00:00:00 2001 From: Yingwei Zheng Date: Mon, 11 Sep 2023 03:58:02 +0800 Subject: [PATCH 1/2] [ValueTracking] Simplify uaddo pattern --- llvm/lib/Analysis/ValueTracking.cpp | 23 .../InstSimplify/and-or-implied-cond.ll | 104 ++ 2 files changed, 127 insertions(+) diff --git a/llvm/lib/Analysis/ValueTracking.cpp b/llvm/lib/Analysis/ValueTracking.cpp index c4153b824c37e0a..5aaff4ee81be969 100644 --- a/llvm/lib/Analysis/ValueTracking.cpp +++ b/llvm/lib/Analysis/ValueTracking.cpp @@ -8291,6 +8291,29 @@ static std::optional isImpliedCondICmps(const ICmpInst *LHS, if (L0 == R0 && match(L1, m_APInt(LC)) && match(R1, m_APInt(RC))) return isImpliedCondCommonOperandWithConstants(LPred, *LC, RPred, *RC); + // L0 = R0 = L1 + R1, L0 >=u L1 implies R0 >=u R1, L0 From 83fa03f89c69a0a13336f6761023bb1415f92505 Mon Sep 17 00:00:00 2001 From: Yingwei Zheng Date: Sun, 24 Sep 2023 17:04:32 +0800 Subject: [PATCH 2/2] fixup! [ValueTracking] Simplify uaddo pattern --- llvm/lib/Analysis/ValueTracking.cpp | 2 +- 1 file changed, 1 insertion(+), 1 deletion(-) diff --git a/llvm/lib/Analysis/ValueTracking.cpp b/llvm/lib/Analysis/ValueTracking.cpp index 5aaff4ee81be969..f2278f3b7097dac 100644 --- a/llvm/lib/Analysis/ValueTracking.cpp +++ b/llvm/lib/Analysis/ValueTracking.cpp @@ -8308,7 +8308,7 @@ static std::optional isImpliedCondICmps(const ICmpInst *LHS, RPred = ICmpInst::getSwappedPredicate(RPred); } if (L0 == R0 && -(LPred == ICmpInst::ICMP_UGE || LPred == ICmpInst::ICMP_ULT) && +(LPred == ICmpInst::ICMP_ULT || LPred == ICmpInst::ICMP_UGE) && (RPred == ICmpInst::ICMP_ULT || RPred == ICmpInst::ICMP_UGE) && match(L0, m_c_Add(m_Specific(L1), m_Specific(R1 return LPred == RPred; ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [ValueTracking] Simplify uaddo pattern (PR #65910)

https://github.com/dtcxzyw resolved https://github.com/llvm/llvm-project/pull/65910 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang-tools-extra] [ValueTracking] Simplify uaddo pattern (PR #65910)

https://github.com/dtcxzyw resolved https://github.com/llvm/llvm-project/pull/65910 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang-tools-extra] [ValueTracking] Simplify uaddo pattern (PR #65910)

@@ -8291,6 +8291,29 @@ static std::optional isImpliedCondICmps(const ICmpInst *LHS, if (L0 == R0 && match(L1, m_APInt(LC)) && match(R1, m_APInt(RC))) return isImpliedCondCommonOperandWithConstants(LPred, *LC, RPred, *RC); + // L0 = R0 = L1 + R1, L0 >=u L1 implies R0 >=u R1, L0 u L1 -> R0 >u R1` and `L0 <=u L1 -> R0 <=u R1`. Alive2: https://alive2.llvm.org/ce/z/VKtFkD https://github.com/llvm/llvm-project/pull/65910 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [ValueTracking] Simplify uaddo pattern (PR #65910)

@@ -8291,6 +8291,29 @@ static std::optional isImpliedCondICmps(const ICmpInst *LHS, if (L0 == R0 && match(L1, m_APInt(LC)) && match(R1, m_APInt(RC))) return isImpliedCondCommonOperandWithConstants(LPred, *LC, RPred, *RC); + // L0 = R0 = L1 + R1, L0 >=u L1 implies R0 >=u R1, L0 u L1 -> R0 >u R1` and `L0 <=u L1 -> R0 <=u R1`. Alive2: https://alive2.llvm.org/ce/z/VKtFkD https://github.com/llvm/llvm-project/pull/65910 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang-tools-extra] [ValueTracking] Simplify uaddo pattern (PR #65910)

https://github.com/dtcxzyw resolved https://github.com/llvm/llvm-project/pull/65910 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang-tools-extra] [InstCombine] Simplify the pattern `a ne/eq (zext/sext (a ne/eq c))` (PR #65852)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/65852

>From d9d8bcbb98e8f5aecb9733329389d61a489bd731 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Sat, 9 Sep 2023 23:07:29 +0800

Subject: [PATCH 1/7] [InstCombine] Simplify the pattern `a ne/eq (zext (a

ne/eq c))`

---

.../InstCombine/InstCombineCompares.cpp | 62 ++

.../test/Transforms/InstCombine/icmp-range.ll | 181 ++

2 files changed, 243 insertions(+)

diff --git a/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

b/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

index 9fdc46fec631679..837b8e6d2619989 100644

--- a/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

+++ b/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

@@ -6309,7 +6309,69 @@ Instruction

*InstCombinerImpl::foldICmpUsingBoolRange(ICmpInst &I) {

Y->getType()->isIntOrIntVectorTy(1) && Pred == ICmpInst::ICMP_ULE)

return BinaryOperator::CreateOr(Builder.CreateIsNull(X), Y);

+ ICmpInst::Predicate Pred1, Pred2;

const APInt *C;

+ // icmp eq/ne X, (zext (icmp eq/ne X, C))

+ if (match(&I, m_c_ICmp(Pred1, m_Value(X),

+ m_ZExt(m_ICmp(Pred2, m_Deferred(X), m_APInt(C) &&

+ ICmpInst::isEquality(Pred1) && ICmpInst::isEquality(Pred2)) {

+if (C->isZero()) {

+ if (Pred2 == ICmpInst::ICMP_EQ) {

+// icmp eq X, (zext (icmp eq X, 0)) --> false

+// icmp ne X, (zext (icmp eq X, 0)) --> true

+return replaceInstUsesWith(

+I,

+Constant::getIntegerValue(

+I.getType(),

+APInt(1U, static_cast(Pred1 == ICmpInst::ICMP_NE;

+ } else {

+// icmp eq X, (zext (icmp ne X, 0)) --> icmp ult X, 2

+// icmp ne X, (zext (icmp ne X, 0)) --> icmp ugt X, 1

+return ICmpInst::Create(

+Instruction::ICmp,

+Pred1 == ICmpInst::ICMP_NE ? ICmpInst::ICMP_UGT

+ : ICmpInst::ICMP_ULT,

+X,

+Constant::getIntegerValue(

+X->getType(), APInt(X->getType()->getScalarSizeInBits(),

+Pred1 == ICmpInst::ICMP_NE ? 1 : 2)));

+ }

+} else if (C->isOne()) {

+ if (Pred2 == ICmpInst::ICMP_NE) {

+// icmp eq X, (zext (icmp ne X, 1)) --> false

+// icmp ne X, (zext (icmp ne X, 1)) --> true

+return replaceInstUsesWith(

+I,

+Constant::getIntegerValue(

+I.getType(),

+APInt(1U, static_cast(Pred1 == ICmpInst::ICMP_NE;

+ } else {

+// icmp eq X, (zext (icmp eq X, 1)) --> icmp ult X, 2

+// icmp ne X, (zext (icmp eq X, 1)) --> icmp ugt X, 1

+return ICmpInst::Create(

+Instruction::ICmp,

+Pred1 == ICmpInst::ICMP_NE ? ICmpInst::ICMP_UGT

+ : ICmpInst::ICMP_ULT,

+X,

+Constant::getIntegerValue(

+X->getType(), APInt(X->getType()->getScalarSizeInBits(),

+Pred1 == ICmpInst::ICMP_NE ? 1 : 2)));

+ }

+} else {

+ // C != 0 && C != 1

+ // icmp eq X, (zext (icmp eq X, C)) --> icmp eq X, 0

+ // icmp eq X, (zext (icmp ne X, C)) --> icmp eq X, 1

+ // icmp ne X, (zext (icmp eq X, C)) --> icmp ne X, 0

+ // icmp ne X, (zext (icmp ne X, C)) --> icmp ne X, 1

+ return ICmpInst::Create(

+ Instruction::ICmp, Pred1, X,

+ Constant::getIntegerValue(

+ X->getType(),

+ APInt(X->getType()->getScalarSizeInBits(),

+static_cast(Pred2 == ICmpInst::ICMP_NE;

+}

+ }

+

if (match(I.getOperand(0), m_c_Add(m_ZExt(m_Value(X)), m_SExt(m_Value(Y

&&

match(I.getOperand(1), m_APInt(C)) &&

X->getType()->isIntOrIntVectorTy(1) &&

diff --git a/llvm/test/Transforms/InstCombine/icmp-range.ll

b/llvm/test/Transforms/InstCombine/icmp-range.ll

index 4281e09cb0309c8..15424fce33fdeea 100644

--- a/llvm/test/Transforms/InstCombine/icmp-range.ll

+++ b/llvm/test/Transforms/InstCombine/icmp-range.ll

@@ -1034,6 +1034,187 @@ define i1 @icmp_ne_bool_1(ptr %ptr) {

ret i1 %cmp

}

+define i1 @icmp_ne_zext_eq_zero(i32 %a) {

+; CHECK-LABEL: @icmp_ne_zext_eq_zero(

+; CHECK-NEXT:ret i1 true

+;

+ %cmp = icmp eq i32 %a, 0

+ %conv = zext i1 %cmp to i32

+ %cmp1 = icmp ne i32 %conv, %a

+ ret i1 %cmp1

+}

+

+define i1 @icmp_ne_zext_ne_zero(i32 %a) {

+; CHECK-LABEL: @icmp_ne_zext_ne_zero(

+; CHECK-NEXT:[[CMP1:%.*]] = icmp ugt i32 [[A:%.*]], 1

+; CHECK-NEXT:ret i1 [[CMP1]]

+;

+ %cmp = icmp ne i32 %a, 0

+ %conv = zext i1 %cmp to i32

+ %cmp1 = icmp ne i32 %conv, %a

+ ret i1 %cmp1

+}

+

+define i1 @icmp_eq_zext_eq_zero(i32 %a) {

+; CHECK-LABEL: @icmp_eq_zext_eq_zero(

+; CHECK-NEXT:ret i1 false

+;

+ %cmp = icmp eq i32 %a, 0

+ %conv = zext i1 %cmp to i32

+ %cmp1 = icmp eq i32 %conv, %a

+ ret i1 %cmp1

+}

+

+define i1 @icmp_eq_zext_ne_zero(i32 %

[clang] [InstCombine] Simplify the pattern `a ne/eq (zext/sext (a ne/eq c))` (PR #65852)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/65852

>From d9d8bcbb98e8f5aecb9733329389d61a489bd731 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Sat, 9 Sep 2023 23:07:29 +0800

Subject: [PATCH 1/7] [InstCombine] Simplify the pattern `a ne/eq (zext (a

ne/eq c))`

---

.../InstCombine/InstCombineCompares.cpp | 62 ++

.../test/Transforms/InstCombine/icmp-range.ll | 181 ++

2 files changed, 243 insertions(+)

diff --git a/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

b/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

index 9fdc46fec631679..837b8e6d2619989 100644

--- a/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

+++ b/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

@@ -6309,7 +6309,69 @@ Instruction

*InstCombinerImpl::foldICmpUsingBoolRange(ICmpInst &I) {

Y->getType()->isIntOrIntVectorTy(1) && Pred == ICmpInst::ICMP_ULE)

return BinaryOperator::CreateOr(Builder.CreateIsNull(X), Y);

+ ICmpInst::Predicate Pred1, Pred2;

const APInt *C;

+ // icmp eq/ne X, (zext (icmp eq/ne X, C))

+ if (match(&I, m_c_ICmp(Pred1, m_Value(X),

+ m_ZExt(m_ICmp(Pred2, m_Deferred(X), m_APInt(C) &&

+ ICmpInst::isEquality(Pred1) && ICmpInst::isEquality(Pred2)) {

+if (C->isZero()) {

+ if (Pred2 == ICmpInst::ICMP_EQ) {

+// icmp eq X, (zext (icmp eq X, 0)) --> false

+// icmp ne X, (zext (icmp eq X, 0)) --> true

+return replaceInstUsesWith(

+I,

+Constant::getIntegerValue(

+I.getType(),

+APInt(1U, static_cast(Pred1 == ICmpInst::ICMP_NE;

+ } else {

+// icmp eq X, (zext (icmp ne X, 0)) --> icmp ult X, 2

+// icmp ne X, (zext (icmp ne X, 0)) --> icmp ugt X, 1

+return ICmpInst::Create(

+Instruction::ICmp,

+Pred1 == ICmpInst::ICMP_NE ? ICmpInst::ICMP_UGT

+ : ICmpInst::ICMP_ULT,

+X,

+Constant::getIntegerValue(

+X->getType(), APInt(X->getType()->getScalarSizeInBits(),

+Pred1 == ICmpInst::ICMP_NE ? 1 : 2)));

+ }

+} else if (C->isOne()) {

+ if (Pred2 == ICmpInst::ICMP_NE) {

+// icmp eq X, (zext (icmp ne X, 1)) --> false

+// icmp ne X, (zext (icmp ne X, 1)) --> true

+return replaceInstUsesWith(

+I,

+Constant::getIntegerValue(

+I.getType(),

+APInt(1U, static_cast(Pred1 == ICmpInst::ICMP_NE;

+ } else {

+// icmp eq X, (zext (icmp eq X, 1)) --> icmp ult X, 2

+// icmp ne X, (zext (icmp eq X, 1)) --> icmp ugt X, 1

+return ICmpInst::Create(

+Instruction::ICmp,

+Pred1 == ICmpInst::ICMP_NE ? ICmpInst::ICMP_UGT

+ : ICmpInst::ICMP_ULT,

+X,

+Constant::getIntegerValue(

+X->getType(), APInt(X->getType()->getScalarSizeInBits(),

+Pred1 == ICmpInst::ICMP_NE ? 1 : 2)));

+ }

+} else {

+ // C != 0 && C != 1

+ // icmp eq X, (zext (icmp eq X, C)) --> icmp eq X, 0

+ // icmp eq X, (zext (icmp ne X, C)) --> icmp eq X, 1

+ // icmp ne X, (zext (icmp eq X, C)) --> icmp ne X, 0

+ // icmp ne X, (zext (icmp ne X, C)) --> icmp ne X, 1

+ return ICmpInst::Create(

+ Instruction::ICmp, Pred1, X,

+ Constant::getIntegerValue(

+ X->getType(),

+ APInt(X->getType()->getScalarSizeInBits(),

+static_cast(Pred2 == ICmpInst::ICMP_NE;

+}

+ }

+

if (match(I.getOperand(0), m_c_Add(m_ZExt(m_Value(X)), m_SExt(m_Value(Y

&&

match(I.getOperand(1), m_APInt(C)) &&

X->getType()->isIntOrIntVectorTy(1) &&

diff --git a/llvm/test/Transforms/InstCombine/icmp-range.ll

b/llvm/test/Transforms/InstCombine/icmp-range.ll

index 4281e09cb0309c8..15424fce33fdeea 100644

--- a/llvm/test/Transforms/InstCombine/icmp-range.ll

+++ b/llvm/test/Transforms/InstCombine/icmp-range.ll

@@ -1034,6 +1034,187 @@ define i1 @icmp_ne_bool_1(ptr %ptr) {

ret i1 %cmp

}

+define i1 @icmp_ne_zext_eq_zero(i32 %a) {

+; CHECK-LABEL: @icmp_ne_zext_eq_zero(

+; CHECK-NEXT:ret i1 true

+;

+ %cmp = icmp eq i32 %a, 0

+ %conv = zext i1 %cmp to i32

+ %cmp1 = icmp ne i32 %conv, %a

+ ret i1 %cmp1

+}

+

+define i1 @icmp_ne_zext_ne_zero(i32 %a) {

+; CHECK-LABEL: @icmp_ne_zext_ne_zero(

+; CHECK-NEXT:[[CMP1:%.*]] = icmp ugt i32 [[A:%.*]], 1

+; CHECK-NEXT:ret i1 [[CMP1]]

+;

+ %cmp = icmp ne i32 %a, 0

+ %conv = zext i1 %cmp to i32

+ %cmp1 = icmp ne i32 %conv, %a

+ ret i1 %cmp1

+}

+

+define i1 @icmp_eq_zext_eq_zero(i32 %a) {

+; CHECK-LABEL: @icmp_eq_zext_eq_zero(

+; CHECK-NEXT:ret i1 false

+;

+ %cmp = icmp eq i32 %a, 0

+ %conv = zext i1 %cmp to i32

+ %cmp1 = icmp eq i32 %conv, %a

+ ret i1 %cmp1

+}

+

+define i1 @icmp_eq_zext_ne_zero(i32 %

[clang] [InstCombine] Simplify the pattern `a ne/eq (zext/sext (a ne/eq c))` (PR #65852)

https://github.com/dtcxzyw resolved https://github.com/llvm/llvm-project/pull/65852 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang-tools-extra] [InstCombine] Simplify the pattern `a ne/eq (zext/sext (a ne/eq c))` (PR #65852)

https://github.com/dtcxzyw resolved https://github.com/llvm/llvm-project/pull/65852 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [ValueTracking] Simplify uaddo pattern (PR #65910)

@@ -8291,6 +8291,29 @@ static std::optional isImpliedCondICmps(const ICmpInst *LHS, if (L0 == R0 && match(L1, m_APInt(LC)) && match(R1, m_APInt(RC))) return isImpliedCondCommonOperandWithConstants(LPred, *LC, RPred, *RC); + // L0 = R0 = L1 + R1, L0 >=u L1 implies R0 >=u R1, L0 https://alive2.llvm.org/ce/z/eWsJH2. https://github.com/llvm/llvm-project/pull/65910 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [ValueTracking] Simplify uaddo pattern (PR #65910)

https://github.com/dtcxzyw unresolved https://github.com/llvm/llvm-project/pull/65910 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [InstCombine] Simplify the pattern `a ne/eq (zext/sext (a ne/eq c))` (PR #65852)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/65852

>From d9d8bcbb98e8f5aecb9733329389d61a489bd731 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Sat, 9 Sep 2023 23:07:29 +0800

Subject: [PATCH 1/8] [InstCombine] Simplify the pattern `a ne/eq (zext (a

ne/eq c))`

---

.../InstCombine/InstCombineCompares.cpp | 62 ++

.../test/Transforms/InstCombine/icmp-range.ll | 181 ++

2 files changed, 243 insertions(+)

diff --git a/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

b/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

index 9fdc46fec631679..837b8e6d2619989 100644

--- a/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

+++ b/llvm/lib/Transforms/InstCombine/InstCombineCompares.cpp

@@ -6309,7 +6309,69 @@ Instruction

*InstCombinerImpl::foldICmpUsingBoolRange(ICmpInst &I) {