[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw closed https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/wangpc-pp approved this pull request. LGTM. https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/20] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap ) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap ) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/20] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap )

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap ) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258,

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -290,8 +290,24 @@ std::string riscv::getRISCVArch(const llvm::opt::ArgList

,

// 2. Get march (isa string) based on `-mcpu=`

if (const Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ // If the target cpu is unrecognized, use target features.

+ if (CPU.empty() || CPU.starts_with("generic")) {

dtcxzyw wrote:

Done.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -290,8 +290,24 @@ std::string riscv::getRISCVArch(const llvm::opt::ArgList

,

// 2. Get march (isa string) based on `-mcpu=`

if (const Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ // If the target cpu is unrecognized, use target features.

+ if (CPU.empty() || CPU.starts_with("generic")) {

wangpc-pp wrote:

I think `CPU` will never be empty now?

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

dtcxzyw wrote: Ping @wangpc-pp @topperc @preames https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/19] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap ) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap ) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/19] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap )

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap ) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258,

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

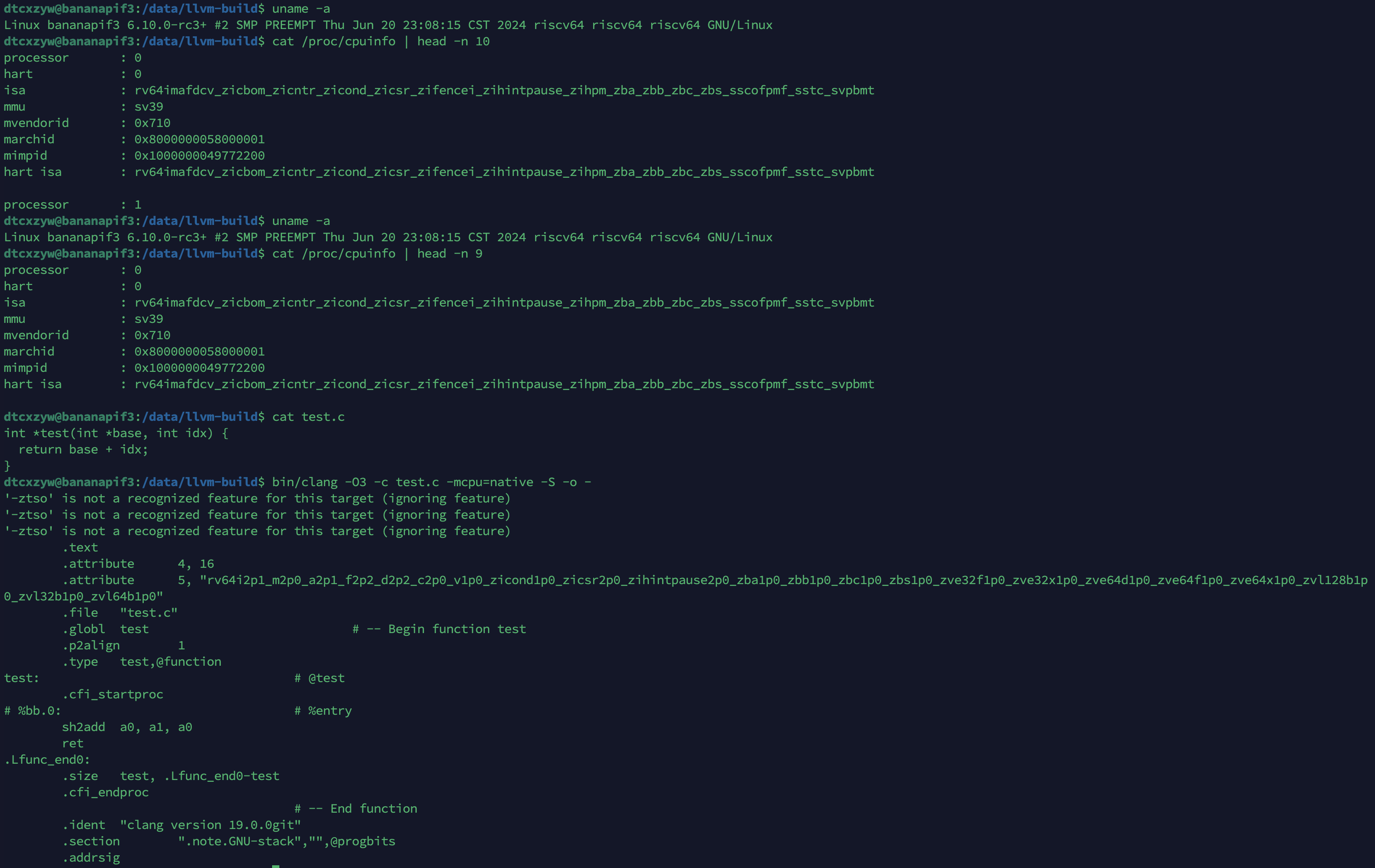

dtcxzyw wrote: ``` dtcxzyw@bananapif3:/data/llvm-build$ bin/clang -mcpu=native --print-enabled-extensions clang version 19.0.0git Target: riscv64-unknown-linux-gnu Thread model: posix InstalledDir: /data/llvm-build/bin Build config: +assertions Extensions enabled for the given RISC-V target Name Version Description i2.1 'I' (Base Integer Instruction Set) m2.0 'M' (Integer Multiplication and Division) a2.1 'A' (Atomic Instructions) f2.2 'F' (Single-Precision Floating-Point) d2.2 'D' (Double-Precision Floating-Point) c2.0 'C' (Compressed Instructions) v1.0 'V' (Vector Extension for Application Processors) zicond 1.0 'Zicond' (Integer Conditional Operations) zicsr2.0 'zicsr' (CSRs) zihintpause 2.0 'Zihintpause' (Pause Hint) zmmul1.0 'Zmmul' (Integer Multiplication) zba 1.0 'Zba' (Address Generation Instructions) zbb 1.0 'Zbb' (Basic Bit-Manipulation) zbc 1.0 'Zbc' (Carry-Less Multiplication) zbs 1.0 'Zbs' (Single-Bit Instructions) zve32f 1.0 'Zve32f' (Vector Extensions for Embedded Processors with maximal 32 EEW and F extension) zve32x 1.0 'Zve32x' (Vector Extensions for Embedded Processors with maximal 32 EEW) zve64d 1.0 'Zve64d' (Vector Extensions for Embedded Processors with maximal 64 EEW, F and D extension) zve64f 1.0 'Zve64f' (Vector Extensions for Embedded Processors with maximal 64 EEW and F extension) zve64x 1.0 'Zve64x' (Vector Extensions for Embedded Processors with maximal 64 EEW) zvl128b 1.0 'Zvl' (Minimum Vector Length) 128 zvl32b 1.0 'Zvl' (Minimum Vector Length) 32 zvl64b 1.0 'Zvl' (Minimum Vector Length) 64 Experimental extensions ISA String: rv64i2p1_m2p0_a2p1_f2p2_d2p2_c2p0_v1p0_zicond1p0_zicsr2p0_zihintpause2p0_zmmul1p0_zba1p0_zbb1p0_zbc1p0_zbs1p0_zve32f1p0_zve32x1p0_zve64d1p0_zve64f1p0_zve64x1p0_zvl128b1p0_zvl32b1p0_zvl64b1p0 dtcxzyw@bananapif3:/data/llvm-build$ ``` https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/18] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap ) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap ) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/18] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap )

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap ) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258,

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

dtcxzyw wrote: I will rebase on the top of https://github.com/llvm/llvm-project/pull/97824. https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/17] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap ) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap ) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/17] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap )

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap ) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258,

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/16] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap ) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap ) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/16] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap )

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap ) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258,

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/topperc approved this pull request. LGTM https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/topperc edited https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -290,8 +290,24 @@ StringRef riscv::getRISCVArch(const llvm::opt::ArgList

,

// 2. Get march (isa string) based on `-mcpu=`

if (const Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ // If the target cpu is unrecognized, use target features.

+ if (CPU.empty() || CPU.starts_with("generic")) {

+llvm::StringMap HostFeatures;

+if (llvm::sys::getHostCPUFeatures(HostFeatures)) {

+ std::vector Features;

+ for (auto : HostFeatures)

+Features.push_back(

+Args.MakeArgString((F.second ? "+" : "-") + F.first()));

topperc wrote:

I don't think this was resolved.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

github-actions[bot] wrote:

:warning: C/C++ code formatter, clang-format found issues in your code.

:warning:

You can test this locally with the following command:

``bash

git-clang-format --diff 902fb1b4653d5a23613492406cd5693446f06ab6

6be7eea2a193ca3d92141f62286f779124647acd --

clang/lib/Driver/ToolChains/Arch/RISCV.cpp llvm/lib/TargetParser/Host.cpp

``

View the diff from clang-format here.

``diff

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index a6c848d180..7b13e68475 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -2063,8 +2063,8 @@ bool sys::getHostCPUFeatures(StringMap ) {

Features["zfa"] = ExtMask & (1ULL << 32); // RISCV_HWPROBE_EXT_ZFA

// TODO: set ztso when it is no longer experimental.

// Features["ztso"] = ExtMask & (1ULL << 33);// RISCV_HWPROBE_EXT_ZTSO

- Features["zacas"] = ExtMask & (1ULL << 34); // RISCV_HWPROBE_EXT_ZACAS

- Features["zicond"] = ExtMask & (1ULL << 35); // RISCV_HWPROBE_EXT_ZICOND

+ Features["zacas"] = ExtMask & (1ULL << 34); // RISCV_HWPROBE_EXT_ZACAS

+ Features["zicond"] = ExtMask & (1ULL << 35); // RISCV_HWPROBE_EXT_ZICOND

Features["zihintpause"] =

ExtMask & (1ULL << 36); // RISCV_HWPROBE_EXT_ZIHINTPAUSE

``

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/14] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap ) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap ) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/14] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap )

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap ) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258,

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -290,8 +290,24 @@ StringRef riscv::getRISCVArch(const llvm::opt::ArgList

,

// 2. Get march (isa string) based on `-mcpu=`

if (const Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ // If the target cpu is unrecognized, use target features.

+ if (CPU.empty() || CPU.starts_with("generic")) {

+llvm::StringMap HostFeatures;

+if (llvm::sys::getHostCPUFeatures(HostFeatures)) {

+ std::vector Features;

+ for (auto : HostFeatures)

+Features.push_back(

+Args.MakeArgString((F.second ? "+" : "-") + F.first()));

topperc wrote:

Do we need MakeArgString here? I thought that was making a string that needs a

longer lifetime to be stored in a StringRef.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -290,8 +290,24 @@ StringRef riscv::getRISCVArch(const llvm::opt::ArgList

,

// 2. Get march (isa string) based on `-mcpu=`

if (const Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ // If the target cpu is unrecognized, use target features.

+ if (CPU.empty() || CPU.starts_with("generic")) {

+llvm::StringMap HostFeatures;

+if (llvm::sys::getHostCPUFeatures(HostFeatures)) {

+ std::vector Features;

+ for (auto : HostFeatures)

+Features.push_back(

+Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+

+ auto ParseResult = llvm::RISCVISAInfo::parseFeatures(

+ Triple.isRISCV32() ? 32 : 64, Features);

+ if (ParseResult)

+return (*ParseResult)->toString();

preames wrote:

Good catch. Returning std::string for now appears to be the path of least

resistance.

Glancing at the callers, I note that more than half immediately call

parseArchString. We could invert the API here, and return the parsed ISAInfo,

and then convert that back into string form on demand. I didn't see any cases

where we wanted the string form of an invalid architecture combination - that

would be the case which might prevent the API inversion.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -290,8 +290,24 @@ StringRef riscv::getRISCVArch(const llvm::opt::ArgList

,

// 2. Get march (isa string) based on `-mcpu=`

if (const Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ // If the target cpu is unrecognized, use target features.

+ if (CPU.empty() || CPU.starts_with("generic")) {

+llvm::StringMap HostFeatures;

+if (llvm::sys::getHostCPUFeatures(HostFeatures)) {

+ std::vector Features;

+ for (auto : HostFeatures)

+Features.push_back(

+Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+

+ auto ParseResult = llvm::RISCVISAInfo::parseFeatures(

+ Triple.isRISCV32() ? 32 : 64, Features);

+ if (ParseResult)

+return (*ParseResult)->toString();

dtcxzyw wrote:

@preames Do you think it is ok to change the return type of

`riscv::getRISCVArch` to `std::string`?

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/13] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap ) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap ) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/13] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap )

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap ) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258,

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -290,8 +290,24 @@ StringRef riscv::getRISCVArch(const llvm::opt::ArgList

,

// 2. Get march (isa string) based on `-mcpu=`

if (const Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ // If the target cpu is unrecognized, use target features.

+ if (CPU.empty() || CPU.starts_with("generic")) {

+llvm::StringMap HostFeatures;

+if (llvm::sys::getHostCPUFeatures(HostFeatures)) {

+ std::vector Features;

+ for (auto : HostFeatures)

+Features.push_back(

+Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+

+ auto ParseResult = llvm::RISCVISAInfo::parseFeatures(

+ Triple.isRISCV32() ? 32 : 64, Features);

+ if (ParseResult)

+return (*ParseResult)->toString();

dtcxzyw wrote:

Sorry, I forget that `riscv::getRISCVArch` returns `StringRef`.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -83,8 +83,14 @@ void riscv::getRISCVTargetFeatures(const Driver , const

llvm::Triple ,

// and other features (ex. mirco architecture feature) from mcpu

if (Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ llvm::StringMap HostFeatures;

+ if (llvm::sys::getHostCPUFeatures(HostFeatures))

+for (auto : HostFeatures)

+ Features.push_back(

+ Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+}

dtcxzyw wrote:

See

https://github.com/llvm/llvm-project/blob/0f5fa3558eb36823c16ba81a4c6e6e23a5f9df24/clang/lib/Driver/ToolChains/Arch/RISCV.cpp#L72-L78.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -83,8 +83,14 @@ void riscv::getRISCVTargetFeatures(const Driver , const

llvm::Triple ,

// and other features (ex. mirco architecture feature) from mcpu

if (Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ llvm::StringMap HostFeatures;

+ if (llvm::sys::getHostCPUFeatures(HostFeatures))

+for (auto : HostFeatures)

+ Features.push_back(

+ Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+}

dtcxzyw wrote:

Done.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/dtcxzyw updated

https://github.com/llvm/llvm-project/pull/94352

>From ff839bef048a65760f4cd0e9abafe11cfebd9362 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 21:08:27 +0800

Subject: [PATCH 01/12] [RISCV] Add support for getHostCPUFeatures using

hwprobe

Co-authored-by: Yangyu Chen

---

llvm/lib/TargetParser/Host.cpp | 68 ++

1 file changed, 68 insertions(+)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index 68155acd9e5bc..b4a13b38eb380 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1998,6 +1998,74 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+#ifdef __has_include

+#if __has_include()

+#include

+#endif

+#endif

+bool sys::getHostCPUFeatures(StringMap ) {

+#ifdef RISCV_HWPROBE_KEY_MVENDORID

+ riscv_hwprobe Query[2]{

+ {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

+ {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

+ };

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

+/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t ExtMask = Query[0].value;

+ Features["f"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["d"] = ExtMask & RISCV_HWPROBE_IMA_FD;

+ Features["c"] = ExtMask & RISCV_HWPROBE_IMA_C;

+ Features["v"] = ExtMask & RISCV_HWPROBE_IMA_V;

+ Features["zba"] = ExtMask & RISCV_HWPROBE_IMA_ZBA;

+ Features["zbb"] = ExtMask & RISCV_HWPROBE_IMA_ZBB;

+ Features["zbs"] = ExtMask & RISCV_HWPROBE_IMA_ZBS;

+ Features["zicboz"] = ExtMask & RISCV_HWPROBE_IMA_ZICBOZ;

+ Features["zbc"] = ExtMask & RISCV_HWPROBE_IMA_ZBC;

+ Features["zbkb"] = ExtMask & RISCV_HWPROBE_IMA_ZBKB;

+ Features["zbkc"] = ExtMask & RISCV_HWPROBE_IMA_ZBKC;

+ Features["zbkx"] = ExtMask & RISCV_HWPROBE_IMA_ZBKX;

+ Features["zknd"] = ExtMask & RISCV_HWPROBE_IMA_ZKND;

+ Features["zkne"] = ExtMask & RISCV_HWPROBE_IMA_ZKNE;

+ Features["zknh"] = ExtMask & RISCV_HWPROBE_IMA_ZKNH;

+ Features["zksed"] = ExtMask & RISCV_HWPROBE_IMA_ZKSED;

+ Features["zksh"] = ExtMask & RISCV_HWPROBE_IMA_ZKSH;

+ Features["zkt"] = ExtMask & RISCV_HWPROBE_IMA_ZKT;

+ Features["zvbb"] = ExtMask & RISCV_HWPROBE_IMA_ZVBB;

+ Features["zvbc"] = ExtMask & RISCV_HWPROBE_IMA_ZVBC;

+ Features["zvkb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKB;

+ Features["zvkg"] = ExtMask & RISCV_HWPROBE_IMA_ZVKG;

+ Features["zvkned"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNED;

+ Features["zvknha"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHA;

+ Features["zvknhb"] = ExtMask & RISCV_HWPROBE_IMA_ZVKNHB;

+ Features["zvksed"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSED;

+ Features["zvksh"] = ExtMask & RISCV_HWPROBE_IMA_ZVKSH;

+ Features["zvkt"] = ExtMask & RISCV_HWPROBE_IMA_ZVKT;

+ Features["zfh"] = ExtMask & RISCV_HWPROBE_IMA_ZFH;

+ Features["zfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZFHMIN;

+ Features["zihintntl"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTNTL;

+ Features["zvfh"] = ExtMask & RISCV_HWPROBE_IMA_ZVFH;

+ Features["zvfhmin"] = ExtMask & RISCV_HWPROBE_IMA_ZVFHMIN;

+ Features["zfa"] = ExtMask & RISCV_HWPROBE_IMA_ZFA;

+ Features["ztso"] = ExtMask & RISCV_HWPROBE_IMA_ZTSO;

+ Features["zacas"] = ExtMask & RISCV_HWPROBE_IMA_ZACAS;

+ Features["zicond"] = ExtMask & RISCV_HWPROBE_IMA_ZICOND;

+ Features["zihintpause"] = ExtMask & RISCV_HWPROBE_IMA_ZIHINTPAUSE;

+

+ uint64_t MisalignedMask = Query[1].value;

+ if (MisalignedMask == RISCV_HWPROBE_MISALIGNED_FAST) {

+Features["unaligned-scalar-mem"] = true;

+Features["unaligned-vector-mem"] = true;

+ }

+

+ return true;

+#else

+ return false;

+#endif

+}

#else

bool sys::getHostCPUFeatures(StringMap ) { return false; }

#endif

>From a2fa6e3d64d3a1e2a8e3a7af91068bdb1fda28b1 Mon Sep 17 00:00:00 2001

From: Yingwei Zheng

Date: Tue, 4 Jun 2024 22:10:55 +0800

Subject: [PATCH 02/12] [RISCV] Address review comments.

---

llvm/lib/TargetParser/Host.cpp | 112 +++--

1 file changed, 52 insertions(+), 60 deletions(-)

diff --git a/llvm/lib/TargetParser/Host.cpp b/llvm/lib/TargetParser/Host.cpp

index b4a13b38eb380..ec275c0a7fded 100644

--- a/llvm/lib/TargetParser/Host.cpp

+++ b/llvm/lib/TargetParser/Host.cpp

@@ -1999,72 +1999,64 @@ bool sys::getHostCPUFeatures(StringMap )

{

return true;

}

#elif defined(__linux__) && defined(__riscv)

-#ifdef __has_include

-#if __has_include()

-#include

-#endif

-#endif

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

bool sys::getHostCPUFeatures(StringMap ) {

-#ifdef RISCV_HWPROBE_KEY_MVENDORID

- riscv_hwprobe Query[2]{

- {RISCV_HWPROBE_KEY_IMA_EXT_0, 0},

- {RISCV_HWPROBE_KEY_CPUPERF_0, 0},

- };

- int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/,

-/*pair_count=*/1, /*cpu_count=*/0, /*cpus=*/0,

/*flags=*/0);

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258,

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -83,8 +83,14 @@ void riscv::getRISCVTargetFeatures(const Driver , const

llvm::Triple ,

// and other features (ex. mirco architecture feature) from mcpu

if (Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ llvm::StringMap HostFeatures;

+ if (llvm::sys::getHostCPUFeatures(HostFeatures))

+for (auto : HostFeatures)

+ Features.push_back(

+ Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+}

wangpc-pp wrote:

> @wangpc-pp @topperc Are there any equivalents of the helper `printMArch`?

No, I think there isn't. You may need to write a helper via

`RISCVISAInfo::parseFeatures` and `RISCVISAInfo::toString()`.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -83,8 +83,14 @@ void riscv::getRISCVTargetFeatures(const Driver , const

llvm::Triple ,

// and other features (ex. mirco architecture feature) from mcpu

if (Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ llvm::StringMap HostFeatures;

+ if (llvm::sys::getHostCPUFeatures(HostFeatures))

+for (auto : HostFeatures)

+ Features.push_back(

+ Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+}

dtcxzyw wrote:

@wangpc-pp @topperc

Are there any equivalents of the helper `printMArch`?

https://github.com/llvm/llvm-project/blob/ba60d8a11af2cdd7e80e2fd968cdf52adcabf5a1/llvm/utils/TableGen/RISCVTargetDefEmitter.cpp#L90-L123

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap ) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

dtcxzyw wrote:

Currently `sys::getHostCPUFeatures` has three callers:

+ clang -> `riscv::getRISCVTargetFeatures`

+ llvm-tools -> `codegen::getFeaturesStr`

+ JIT users -> `JITTargetMachineBuilder::detectHost`

I don't think there are any opportunities to reuse the result.

BTW, https://github.com/llvm/llvm-project/pull/85790 may benefit from the vDSO

symbol, but it implements caching itself.

I didn't use the glibc call `__riscv_hwprobe` since `sys/hwprobe.h` was

unavailable on my RV board :(

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/preames approved this pull request. LGTM w/minor comments https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -83,8 +83,14 @@ void riscv::getRISCVTargetFeatures(const Driver , const

llvm::Triple ,

// and other features (ex. mirco architecture feature) from mcpu

if (Arg *A = Args.getLastArg(options::OPT_mcpu_EQ)) {

StringRef CPU = A->getValue();

-if (CPU == "native")

+if (CPU == "native") {

CPU = llvm::sys::getHostCPUName();

+ llvm::StringMap HostFeatures;

+ if (llvm::sys::getHostCPUFeatures(HostFeatures))

+for (auto : HostFeatures)

+ Features.push_back(

+ Args.MakeArgString((F.second ? "+" : "-") + F.first()));

+}

preames wrote:

Do we also need to update riscv::getRISCVArch? There's analogous logic there

for getting features from mcpu native.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap ) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

+/*pair_count=*/std::size(Query), /*cpu_count=*/0,

+/*cpus=*/0, /*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t BaseMask = Query[0].Value;

+ // Check whether RISCV_HWPROBE_BASE_BEHAVIOR_IMA is set.

+ if (BaseMask & 1) {

+Features["i"] = true;

+Features["m"] = true;

+Features["a"] = true;

+ }

+

+ uint64_t ExtMask = Query[1].Value;

+ Features["f"] = ExtMask & (1 << 0); // RISCV_HWPROBE_IMA_FD

+ Features["d"] = ExtMask & (1 << 0); // RISCV_HWPROBE_IMA_FD

+ Features["c"] = ExtMask & (1 << 1); // RISCV_HWPROBE_IMA_C

+ Features["v"] = ExtMask & (1 << 2); // RISCV_HWPROBE_IMA_V

+ Features["zba"] = ExtMask & (1 << 3); // RISCV_HWPROBE_EXT_ZBA

+ Features["zbb"] = ExtMask & (1 << 4); // RISCV_HWPROBE_EXT_ZBB

+ Features["zbs"] = ExtMask & (1 << 5); // RISCV_HWPROBE_EXT_ZBS

+ Features["zicboz"] = ExtMask & (1 << 6); // RISCV_HWPROBE_EXT_ZICBOZ

+ Features["zbc"] = ExtMask & (1 << 7); // RISCV_HWPROBE_EXT_ZBC

+ Features["zbkb"] = ExtMask & (1 << 8);// RISCV_HWPROBE_EXT_ZBKB

+ Features["zbkc"] = ExtMask & (1 << 9);// RISCV_HWPROBE_EXT_ZBKC

+ Features["zbkx"] = ExtMask & (1 << 10); // RISCV_HWPROBE_EXT_ZBKX

+ Features["zknd"] = ExtMask & (1 << 11); // RISCV_HWPROBE_EXT_ZKND

+ Features["zkne"] = ExtMask & (1 << 12); // RISCV_HWPROBE_EXT_ZKNE

+ Features["zknh"] = ExtMask & (1 << 13); // RISCV_HWPROBE_EXT_ZKNH

+ Features["zksed"] = ExtMask & (1 << 14); // RISCV_HWPROBE_EXT_ZKSED

+ Features["zksh"] = ExtMask & (1 << 15); // RISCV_HWPROBE_EXT_ZKSH

+ Features["zkt"] = ExtMask & (1 << 16);// RISCV_HWPROBE_EXT_ZKT

+ Features["zvbb"] = ExtMask & (1 << 17); // RISCV_HWPROBE_EXT_ZVBB

+ Features["zvbc"] = ExtMask & (1 << 18); // RISCV_HWPROBE_EXT_ZVBC

+ Features["zvkb"] = ExtMask & (1 << 19); // RISCV_HWPROBE_EXT_ZVKB

+ Features["zvkg"] = ExtMask & (1 << 20); // RISCV_HWPROBE_EXT_ZVKG

+ Features["zvkned"] = ExtMask & (1 << 21); // RISCV_HWPROBE_EXT_ZVKNED

+ Features["zvknha"] = ExtMask & (1 << 22); // RISCV_HWPROBE_EXT_ZVKNHA

+ Features["zvknhb"] = ExtMask & (1 << 23); // RISCV_HWPROBE_EXT_ZVKNHB

+ Features["zvksed"] = ExtMask & (1 << 24); // RISCV_HWPROBE_EXT_ZVKSED

+ Features["zvksh"] = ExtMask & (1 << 25); // RISCV_HWPROBE_EXT_ZVKSH

+ Features["zvkt"] = ExtMask & (1 << 26); // RISCV_HWPROBE_EXT_ZVKT

+ Features["zfh"] = ExtMask & (1 << 27);// RISCV_HWPROBE_EXT_ZFH

+ Features["zfhmin"] = ExtMask & (1 << 28); // RISCV_HWPROBE_EXT_ZFHMIN

+ Features["zihintntl"] = ExtMask & (1 << 29); // RISCV_HWPROBE_EXT_ZIHINTNTL

+ Features["zvfh"] = ExtMask & (1 << 30); // RISCV_HWPROBE_EXT_ZVFH

+ Features["zvfhmin"] = ExtMask & (1ULL << 31); // RISCV_HWPROBE_EXT_ZVFHMIN

+ Features["zfa"] = ExtMask & (1ULL << 32); // RISCV_HWPROBE_EXT_ZFA

+ // TODO: set ztso when it is no longer experimental.

+ // Features["ztso"] = ExtMask & (1ULL << 33);// RISCV_HWPROBE_EXT_ZTSO

preames wrote:

I agree that leaving this as a TODO is the right thing to do right now.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap ) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

preames wrote:

Consider this a purely stylistic comment.

We should probably be using either the vDSO symbol or the glibc shim. In

either case, we'd have a weak symbol which could possibly be nullptr, and need

to return early.

In this use case, the difference likely doesn't matter, but if we reuse this

code, the lack of caching provided by vDSO could be problematic.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap ) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

+/*pair_count=*/std::size(Query), /*cpu_count=*/0,

+/*cpus=*/0, /*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t BaseMask = Query[0].Value;

+ // Check whether RISCV_HWPROBE_BASE_BEHAVIOR_IMA is set.

+ if (BaseMask & 1) {

+Features["i"] = true;

+Features["m"] = true;

+Features["a"] = true;

+ }

+

+ uint64_t ExtMask = Query[1].Value;

preames wrote:

I think this is likely to be fine in practice.

>From https://docs.kernel.org/arch/riscv/hwprobe.html, I see "If a key is

>unknown to the kernel, its key field will be cleared to -1, and its value set

>to 0. " If I'm reading that properly, if RISCV_HWPROBE_KEY_IMA_EXT_0 isn't a

>valid key, it is the kernel's responsible for clearing all bits to zero, so

>this code should work.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/preames edited https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

https://github.com/topperc approved this pull request. LGTM https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

dtcxzyw wrote: Any thoughts? Hopefully I can catch up with the 19 release :) https://github.com/llvm/llvm-project/pull/94352 ___ cfe-commits mailing list cfe-commits@lists.llvm.org https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap ) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

+/*pair_count=*/std::size(Query), /*cpu_count=*/0,

+/*cpus=*/0, /*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t BaseMask = Query[0].Value;

+ // Check whether RISCV_HWPROBE_BASE_BEHAVIOR_IMA is set.

+ if (BaseMask & 1) {

+Features["i"] = true;

+Features["m"] = true;

+Features["a"] = true;

+ }

+

+ uint64_t ExtMask = Query[1].Value;

dtcxzyw wrote:

FYI, openjdk still uses the value in `RISCV_HWPROBE_KEY_IMA_EXT_0` even if

`RISCV_HWPROBE_BASE_BEHAVIOR_IMA` is not set.

See

https://github.com/openjdk/jdk/blob/e527e1c32fcc7b2560cec540bcde930075ac284a/src/hotspot/os_cpu/linux_riscv/riscv_hwprobe.cpp#L142-L185.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap ) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

+/*pair_count=*/std::size(Query), /*cpu_count=*/0,

+/*cpus=*/0, /*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t BaseMask = Query[0].Value;

+ // Check whether RISCV_HWPROBE_BASE_BEHAVIOR_IMA is set.

+ if (BaseMask & 1) {

+Features["i"] = true;

+Features["m"] = true;

+Features["a"] = true;

+ }

+

+ uint64_t ExtMask = Query[1].Value;

cyyself wrote:

I think this is not safe. The minimal ISA for RISC-V Linux is IMA. If someone

modified the kernel to run on some CPUs without M or A extension(theoretically

A can be replaced with Zalrsc), the base behavior probe will be zero but it

doesn’t mean we have IMA.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap ) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

+/*pair_count=*/std::size(Query), /*cpu_count=*/0,

+/*cpus=*/0, /*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t BaseMask = Query[0].Value;

+ // Check whether RISCV_HWPROBE_BASE_BEHAVIOR_IMA is set.

+ if (BaseMask & 1) {

+Features["i"] = true;

+Features["m"] = true;

+Features["a"] = true;

+ }

+

+ uint64_t ExtMask = Query[1].Value;

topperc wrote:

If the base behavior isn't `RISCV_HWPROBE_BASE_BEHAVIOR_IMA`, can we still use

the value in `RISCV_HWPROBE_KEY_IMA_EXT_0`? It has IMA in its name.

https://github.com/llvm/llvm-project/pull/94352

___

cfe-commits mailing list

cfe-commits@lists.llvm.org

https://lists.llvm.org/cgi-bin/mailman/listinfo/cfe-commits

[clang] [llvm] [RISCV] Add support for getHostCPUFeatures using hwprobe (PR #94352)

@@ -2002,6 +2003,76 @@ bool sys::getHostCPUFeatures(StringMap ) {

return true;

}

+#elif defined(__linux__) && defined(__riscv)

+// struct riscv_hwprobe

+struct RISCVHwProbe {

+ int64_t Key;

+ uint64_t Value;

+};

+bool sys::getHostCPUFeatures(StringMap ) {

+ RISCVHwProbe Query[]{{/*RISCV_HWPROBE_KEY_BASE_BEHAVIOR=*/3, 0},

+ {/*RISCV_HWPROBE_KEY_IMA_EXT_0=*/4, 0}};

+ int Ret = syscall(/*__NR_riscv_hwprobe=*/258, /*pairs=*/Query,

+/*pair_count=*/std::size(Query), /*cpu_count=*/0,

+/*cpus=*/0, /*flags=*/0);

+ if (Ret != 0)

+return false;

+

+ uint64_t BaseMask = Query[0].Value;

+ // Check whether RISCV_HWPROBE_BASE_BEHAVIOR_IMA is set.

+ if (BaseMask & 1) {

+Features["i"] = true;

+Features["m"] = true;

+Features["a"] = true;

+ }

+

+ uint64_t ExtMask = Query[1].Value;

+ Features["f"] = ExtMask & (1 << 0); // RISCV_HWPROBE_IMA_FD

+ Features["d"] = ExtMask & (1 << 0); // RISCV_HWPROBE_IMA_FD

+ Features["c"] = ExtMask & (1 << 1); // RISCV_HWPROBE_IMA_C

+ Features["v"] = ExtMask & (1 << 2); // RISCV_HWPROBE_IMA_V

+ Features["zba"] = ExtMask & (1 << 3); // RISCV_HWPROBE_EXT_ZBA

+ Features["zbb"] = ExtMask & (1 << 4); // RISCV_HWPROBE_EXT_ZBB

+ Features["zbs"] = ExtMask & (1 << 5); // RISCV_HWPROBE_EXT_ZBS