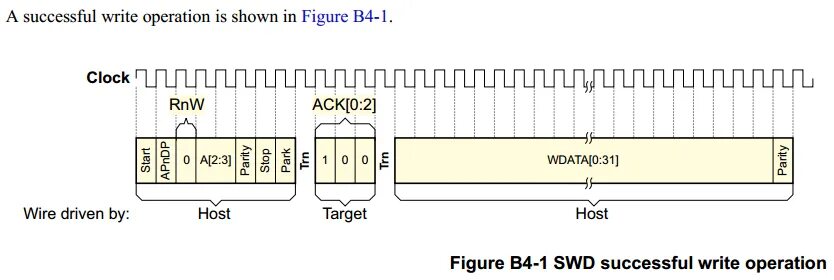

Judging by the cyclogram from the analyzer, it is possible that the adapter does not correctly set the SWDIO bits in relation to the SWCLK clock signal. When transmitting from the adapter, the SWDIO bits are set when the SCLK clock signal drops from 1 to 0 (falling edge), although on the found protocol waveforms, the SWDIO data should be set when the difference is from 0 to 1 (rising edge), and read along the falling edge. At the same time, the device sets the bits on the correct SWCLK edge. Can someone fix it?

--- **[tickets:#456] aducm360 swd could not find MEM-AP** **Status:** new **Milestone:** 0.10.0 **Labels:** aducm360_swd **Created:** Tue Jul 01, 2025 01:58 PM UTC by Den **Last Updated:** Tue Jul 01, 2025 01:58 PM UTC **Owner:** nobody **Attachments:** - [attach.zip](https://sourceforge.net/p/openocd/tickets/456/attachment/attach.zip) (751.5 kB; application/x-zip-compressed) aducm360 not connect to openocd via jtag-swd. adapter based on ftdi2232 used original config aducm360.cfg used my config ftdi_swd.cfg tested in openocd v10 & v12 command: openocd.exe -d0 -f \interface\ftdi\ftdi_swd.cfg -f target\aducm360.cfg -c init -c targets -c "reset halt" -c "flash erase 0" -c shutdown log: debug_level: 0 cortex_m reset_config vectreset Error: [aducm360.cpu] Could not find MEM-AP to control the core TargetName Type Endian TapName State -- ------------------ ---------- ------ ------------------ ------------ 0* aducm360.cpu cortex_m little aducm360.cpu unknown Error: [aducm360.cpu] Could not find MEM-AP to control the core Error: [aducm360.cpu] Debug AP not available, reset NOT asserted! in attach log from debug level 3 ftdi_swd.cfg log saleae logic 1.2.18 --- Sent from sourceforge.net because [email protected] is subscribed to https://sourceforge.net/p/openocd/tickets/ To unsubscribe from further messages, a project admin can change settings at https://sourceforge.net/p/openocd/admin/tickets/options. Or, if this is a mailing list, you can unsubscribe from the mailing list.